# Ahsanullah University of Science and Technology Department of Electrical and Electronic Engineering

# LABORATORY MANUAL FOR ELECTRICAL AND ELECTRONIC SESSIONAL COURSES

Student Name : Student ID :

Course No. : EEE 4232 Course Title : VLSI II Lab.

For the students of Department of Electrical and Electronic Engineering 4<sup>th</sup> Year, 2<sup>nd</sup> Semester

# **Table of Contents**

| Lab-0: Overview of VLSI-II Laboratory                                                    |

|------------------------------------------------------------------------------------------|

| Lab-1: Introduction to Verilog HDL Programming 6                                         |

| Lab-2: Introduction to Functional Verification Using Verilog Testbench                   |

| Lab-3: Modeling Sequential Systems and Finite State Machine Using Verilog HDL 49         |

| Lab-4: Introduction to Unix Shell                                                        |

| Lab-5: Synthesis using Genus Synthesis Solution                                          |

| Lab-6: Physical Design Using Innovus Implementation System (Part 1)                      |

| Lab-7A: Physical Design Using Innovus Implementation System (Part 2)                     |

| Lab-7B: Static Timing Analysis Using Innovus Implementation System                       |

| Lab-8: Physical Verification and Exporting GDSII Using Innovus Implementation System 119 |

| References and Acknowledgment                                                            |

# Lab-0: Overview of VLSI-II Laboratory

# **Objective**

The main objectives of this lab are:

- Familiarization with Application Specific Integrated Circuits (ASIC) design flow.

- Overview of the VLSI-II lab.

#### Introduction

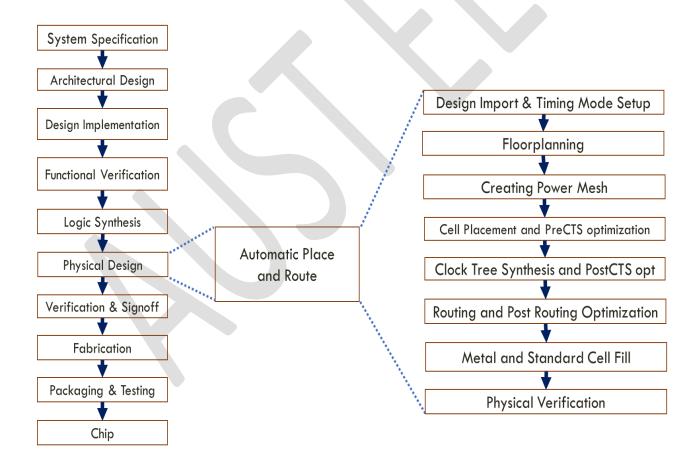

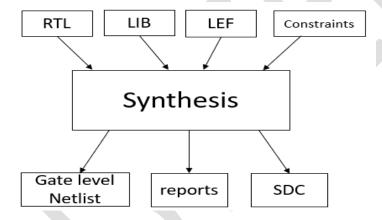

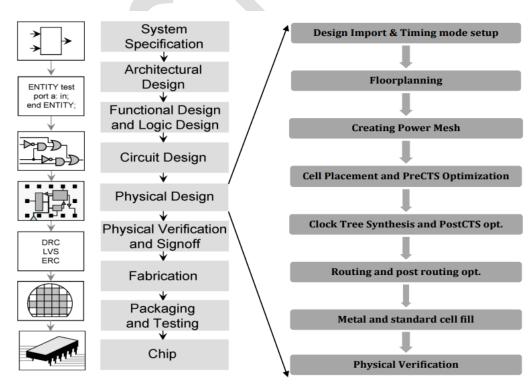

To design very large-scale integrated circuits some frontend and backend processes needed to be acomplished. The processes can be represented as a flow chart to show the life cycle of a chip which is called Application Specific Integrated Circuits (ASIC) design flow. A typical ASIC design flow is shown below.

Figure: ASIC design flow

#### **System Specification**

Design functionality, performance factors (speed, power, latency, throughput, dimension, data size), cost, I/O requirements etc are clearly stated at this stage.

#### **Architectural Design**

Determines required different architecture blocks to implement the design to maximize the performance factors. It also determines the algorithm for optimized connection of the blocks and formal verification is performed.

#### **Design Implementation**

The system can be designed in two ways: analog design and digital design. In the analog design process, circuit blocks are designed at the transistor level. On the other hand, the synthesizable RTL description of the device is programmed using Hardware Description Language (HDL) in the digital design process. HDL Programming can be easily implemented for any modern complex device as it gives the advantage of simulating and verifying the design output and functionality efficiently.

#### **Functional Verification and Testing**

Functional simulation is performed in this stage, and the logic of the system is verified using timing simulation and test vectors. If the functionality doesn't match the Function should be designed again

# **Logic Synthesis**

The process of translating the RTL into a gate-level netlist is called Synthesis. In this process, the design is optimized, and technology mapping or library binding is done. The gate-level netlist must undergo formal verification to prove that RTL and netlist are equivalent.

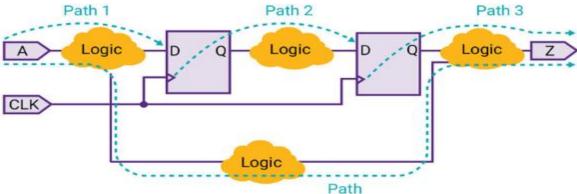

# **Physical Design**

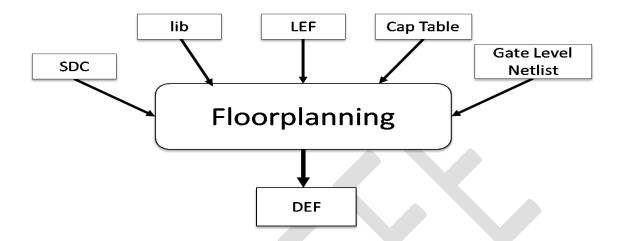

Physical Design is the process of transforming a circuit description into a physical layout that describes the position of cells and routes for the interconnections between them. The physical design consists of the following steps.

- Design Import & Timing Mode Setup

- Floorplanning

- Creating Power Mesh

- Cell Placement and PreCTS optimization

- Clock Tree Synthesis and PostCTS opt

- Routing and Post-Routing Optimization

- Metal and Standard Cell Fill

#### **Verification and Signoff**

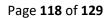

Verification would either be just before the tapeout stage of the chip or the stage where design is again taken back through the same flow for optimization. The following verifications are usually performed in this stage.

- Design Rule Check (DRC): It checks design rules such as shapes/size/spacing and many other complex rules of each metal layer.

- Layout vs Schematic (LVS): It checks whether the design layout is equivalent to its schematic.

- Antenna Rule Check (ARC): Checks for a large area of metals that might affect the manufacturing process.

- Electrical Rule Check (ERC): The methodology used to check the robustness of a design both at schematic and layout levels against various electronic design rules.

After all verifications, post-processing is applied where the physical layout data is translated into an industry-standard format called **GDSII**. The GDSII file is sent to the semiconductor foundry to convert it into mask data which is called **tapeout**. GDS II is a database file format that is the industry standard for data exchange of integrated circuit or IC layout artwork. It is a binary file format representing planar geometric shapes, text labels, and other information about the layout in hierarchical form. It is also referred as Graphic Design System.

#### **Fabrication**

The mask of physical design is sent to factories called fabs(clean room). Several masks are used in turn, each one reproducing a layer of the completed design Masks are used to create a specific pattern of each material in a sequential manner and create a complex pattern of several layers Introduction

For fabricating an IC in the clean room following steps are performed.

- Wafer Preparation

- Oxidation

- Lithography (Photoresist & Masking)

- Etching

- Dopant Incorporation (Diffusion & Ion Implantation)

- Crystal Epitaxial Growth

- Deposition

- Isolation

- Cleaning

#### Packaging & Testing

After fabricating the chip in a clean room, it should pass some specific tests before commercial use. If all test is confirmed it is packaged and sent to the consumer.

# Chip

The final output of the process is a chip.

#### **EDA Files**

# **Liberty Timing File (.lib file)**

ASCII representation of the timing and power parameters associated with any cell in particular semiconductor technology. Types of lib file Fast lib, Slow lib, and Typical lib. Basic differences among those libraries are Nominal voltage Nominal temperature cell leakage Power Capacitance, Fall power, Rise power, and Timing.

# **Library Exchange Format (.lef file)**

LEF is a specification file for representing the physical layout of an IC in an ASCII format. It contains library information for a class of designs. It mainly contains Layer information, Via information, Placement site type and origin, and Macrocell definitions.

### **SDC (Standard Design Constraint)**

The Standard Design Constraint format is used to specify the design intent, including the timing, power and area constraints for a design.

### **Cap table**

Cap table contains information of parasitic Resistance and Capacitance which is used to model the interconnect of a design.

# **Cdb (Celtic Database)**

For signal integrity analysis besides lib files, the tool required the .cdb files also. The main issues of concern for signal integrity are Ringing, Crosstalk, Ground bounce, Distortion, Signal loss, Power supply noise.

# **Commonly used EDA Tools**

| Function                       | Tools                                     |

|--------------------------------|-------------------------------------------|

| Analog Design                  | Cadence Virtuoso, HSPice, LTSpice         |

| Cell Layout Design             | Cadence Virtuoso Layout Suit              |

| RTL Coding                     | Cadence NCSim, ModelSim, Quartus          |

| Synthesis                      | Cadence Genus, Yosys Open Synthesis Suite |

| Physical System Design and STA | Cadence Encounter, Innovus                |

| Verification                   | Cadence PVS, Mentor graphic Calibre       |

# **Probable List of Lab Tasks**

The following processes of VLSI ASIC design flow will be covered in the upcoming classes.

# **Front End Process**

- Verilog HDL programming language.

- Functional Verification using Verilog Testbench.

- Modeling Sequential Systems and FSM using Verilog.

- Synthesis

# **Backend Process**

- Physical Design

- Static Timing Analysis

- Physical Verification and Power Analysis

# **Assessment Procedure and Marks Distribution (Tentative)**

| Assessment Type           | Percentage |

|---------------------------|------------|

| i) Continuous Performance | 10         |

| ii) Lab Test-1            | 20         |

| iii) Lab Test-2           | 25         |

| iv) Assignment            | 15         |

| v) Project                | 30         |

| Total                     | 100        |

# Lab-1: Introduction to Verilog HDL Programming

# **Objective**

The main objectives of this lab are:

- Basic terminology of Verilog HDL programming.

- Familiarization with different levels of Abstraction in Verilog HDL.

- Simulating Verilog HDL using ModelSim.

#### Introduction

A system or chip can be designed in two ways: analog design and digital design. In the analog design process, circuit blocks are designed at the transistor level. Nowadays high performing chips are designed with more smarter functions and that has increased the density of the transistor in a chip. In VLSI (Very Large-Scale Integration) technology chips are designed with more than 100,000 transistors. So it is not easy to design and verify such a complex system in an analog process. In the digital design process, according to the functionality of a chip, a synthesizable RTL description of the system is modeled using the Hardware Description Language (HDL). HDL gives the advantage of simulating and verifying the design output and functionality easily before they were fabricated on chips. For a long time, programming languages such as FORTRAN, Pascal, and C were used to describe sequential computer programs after that Hardware Description Languages (HDLs) came into existence to model the concurrency processes found in hardware elements. Some common HDLs are Verilog, System Verilog, VHDL, VerilogA.

# **Verilog Module**

Modules are the building blocks of the Verilog design. Modules can be embedded within other modules, and a higher level module can communicate with its lower-level modules using their input and output ports. A module should be enclosed within a module and **endmodule** keywords. The following figure shows the structure of any Verilog module.

```

module module_name [(port_name{, port_name})];

[parameter declarations]

[input declarations]

[output declarations]

[inout declarations]

[wire or tri declarations]

[reg or integer declarations]

[function or task declarations]

[assign continuous assignments]

[initial block]

[always blocks]

[gate instantiations]

[module instantiations]

endmodule

```

# **Port Types**

Port provides the interface by which a module can communicate with the internal and external environment. Based on the direction of the signal Verilog language allows three types of ports. Ports can be declared as follows.

| Type of Port       | Verilog Keyword |

|--------------------|-----------------|

| Input port         | input           |

| Output port        | output          |

| Bidirectional port | inout           |

# **Data Types**

Verilog language has two primary data types called Nets and Registers.

#### 1. Nets

- Represents structural connections between components.

- Declared as 'wire'.

- By default, one bit.

- All port declaration are implicitly declared as wire in Verilog

#### 2. Registers

- Represents the variables used to store data.

- Declared as 'reg'.

- Stores/holds the last assigned value until it is changed.

- Must use register data type if a signal is assigned in procedural

In Verilog, "parameter" is used to declare constants and does not belong to any other data type such as register or net data types. A constant expression refers to a constant number or previously defined parameter. We cannot modify parameter values at runtime, but we can modify a parameter value using the "defparam" statement. In modern RTL design, "localparam" is used to declare constants.

#### **Port Connection Rule**

Verilog simulator shows violations if port connection rules are violated.

#### 1. Input

- Internal input ports must always be **net (wire)** type.

- External input ports can be connected to **reg** or **net** type.

#### 2. Output

- Internal output ports can be either reg or net type.

- External outputs must be net type.

#### 3. Inouts

- Internally and externally inout ports must be net type.

- They are bidirectional.eg-power, ground, etc.

#### 4. Width Matching

It is legal to connect internal and external items of different sizes when inter-module port connections. However, a warning is typically issued that the width does not match.

#### 5. Unconnected Ports

Verilog allows ports to remain unconnected. For example, a full adder module has three inputs (A, B, C) and two outputs (sum, carry). So, if we don't want to use any of the inputs or outputs during the submodule call, we simply ignore that by keeping the place blank. Example if a module is full\_add(A, B, C, SUM, Carry) during the submodule call if we want to ignore the C input can write as full\_add a1(x,y, ,z,l)

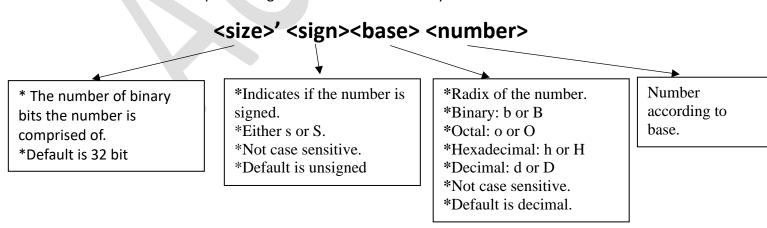

#### Literals

Literals are used for representing constant numbers. The syntax for a constant is shown below.

The following example demonstrates the Verilog syntax for different literals and data types.

```

parameter a,b,c,d,e,f,g,h; // declaration of multiple variables of parameter type

2

reg [7:0]i;

// reg type variable declaration which can store up to 8-bit

3

reg[7:0]j;

// reg type variable declaration which can store up to 8-bit

4

a=549;

// decimal number 549, no size specified

5

b=4'bx;

//4-bit unknow value xxxx

// 8-bit number equivalent to 8b1111 xxx

c=8'hfx;

7

d='h8FF;

// hex number, no size specified

e=5'd3;

// 5-bit decimal number 00011

f=8'b00001011;

//8-bit binary number 00001011

10

g=8'b0000 1011;

// " " is a separator used to improve the readability of 8-bit number 00001011

11

h=8'b1011;

//8-bit binary number 00001011

// 4-bit positive signed number 00001011

12

i=4'sb1011;

//initializes with 1011 then for negative sign 2s complement is performed which

13

j= - 4'sb1011;

is 0101 then 4 zeros are padded for signed value 00000101

```

Example 01 is not a complete Verilog Module it just demonstrates the syntax

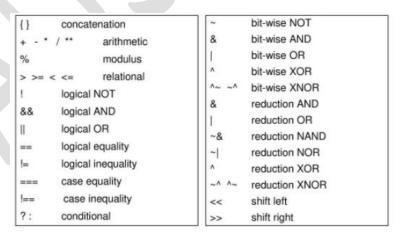

# **Verilog Operators**

To represent the functionality of a digital system different operators such as logical, bitwise, etc. operators must be used. In the following table, different Verilog operators are shown.

#### Table demonstrating different operators

The following example demonstrates the basic logical syntax of basic logical operation used in digital system representation. We can represent the logical expressions in two ways called **Gate Instantiations** and **Continuous Assignment.**

```

1

module gates(A,B, Yn,Ya,Yo,Yx, Zn,Za,Zo,Zx);

// Gate Instantiations

output Yn, Ya, Yo, Yx;

input A, B;

not g1(Yn,A);

and g2(Ya,A,B);

or g3(Yo,A,B);

xor g4(Yx,A,B);

// Continuous Assignment

output Zn,Za,Zo,Zx;

10

11

assign Zn=~A;

12

assign Za=A&B;

13

assign Zo=A | B;

14

assign Zx=A^B;

15

endmodule

```

# **Verilog Modeling Styles**

Digital systems are generally modeled in four ways called **Switch-level modeling**, **Gate level or structural modeling**, **Data flow modeling** (**DFM**), and **Behavioral modeling**.

**N.B:** RTL is a combination of Data Flow and Behavior Modeling styles. The logic synthesis tool can generate a gate-level netlist from RTL.

# 1. Switch level Modeling

This method provides mechanisms for modeling MOS transistors using Verilog. This modeling style is used in very specific cases, for designing leaf cells in a hierarchical design. Switch-level modeling is not detailed enough to catch many of the problems.

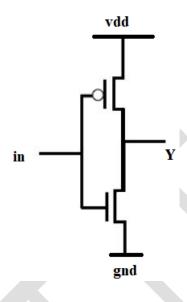

The following example demonstrates the Verilog HDL code of an CMOS inverter using the switch level abstraction.

CMOS Inverter

```

module inv_cmos(in,Y);

input in;

output Y;

supply1 vdd;

supply0 gnd;

pmos p1(Y,vdd,in);

nmos n1(Y,gnd,in);

endmodule

```

# 2. Gate level or structural modeling

In this method, a system is designed using predefined gates or user-defined primitives. It is white box modeling because every design is visible inside the design. It is the lower level of abstraction.

The following example demonstrates the Verilog HDL code of a two to one multiplexer module using the gate level abstraction.

```

1

/*

Steps for Gate Level Modeling

3

I. Develop the Boolean function of output

II.Draw the logic diagram.

5

III.Connect the gates with nets(wires).

6

7

module mux_2to1(s,I0,I1,Y);

input s,I0,I1;

output Y;

10

wire w1,w2,w3;

11

not g1(w1,s);

12

and g2(w2,I0,w1);

13

and g3(w3,s,l1);

14

or g4(Y,w2,w3);

endmodule

15

```

### 3. Data flow modeling (DFM)

In this method, a system is designed by specifying the data flow between input and output. It uses continuous assignment statements to drive a value on a net or wire. It is a higher level of abstraction than the gate level. It may be either black-box modeling or white-box modeling depending on the design complexity.

# **Example 05**

The following example demonstrates the Verilog HDL code of a two to one multiplexer module using the data flow modeling.

```

1

Steps for Data Flow Modeling

I.Obtain the relation between output and input.

II.Impalement the logical relation using "assign" statement.

4

5

*/

module mux_2to1(s,I0,I1,Y);

input s,I0,I1;

output Y;

wire w1,w2,w3;

assign w1=~s;

10

11

assign w2=I0 & w1;

12

assign w3=s & I1;

13

assign Y=w2 | w3;

endmodule

14

```

# 4. Behavioral modeling

In this method, a system is designed and implemented in terms of a design algorithm based on the behavior of the design and its performance. Verilog behavioral code must be inside procedural statements/blocks only. It is the highest level of abstraction. It is also known as black-box modeling.

#### **Procedural Block**

There are two types of procedural blocks in Verilog called "Initial" and "always" blocks. Procedural blocks are evaluated in the order in which they appear in the code that's why it is also known as sequential statements. Procedural statements assign values to reg, integer, real or time variables. Procedural blocks cannot assign values to nets.

#### a) "initial" Block

- Statements inside the initial block are executed only once.

- Executes at time zero.

- Used in Test bench

# b) "always" Block

- Sensitivity list or list of signals that directly affect the output result must be defined in always block.

- Whenever the value of a signal in the sensitivity list changes then the statements inside the always block is executed.

```

always @ (sensitivity_list)

begin

[procedural assignment statement]

[if-else statement]

[case statement]

[while, repeat and for loops]

[task and function calls]

end

```

# Example 06

The following example demonstrates the Verilog HDL code of a two to one multiplexer module using the behavioral modeling style. The always procedural block is used here to set the output of multiplexer(y) whenever any of the inputs (Io and I1) or selection input (s) changes.

```

1 /

```

<sup>2 |</sup> Steps for Behavioral Modeling

<sup>3</sup> I.Develop a behavioral algorithm (like 'C' programming).

```

II.According to the algorithm insert the behavioral statements inside the appropriate procedural

5

block

6

7

module mux_2to1(s,I0,I1,Y);

input s,I0,I1;

8

output reg Y;

9

always@ (s,I0,I1) //if we use always @* The * operator will automatically identify all sensitive variables.

10

11

begin

12

if(s==0)

Y=10;

13

14

else

15

Y=I1;

16

end

endmodule

17

```

# **Hierarchical Modeling**

A Hierarchical methodology is used to design simple components to construct more complex components There are two design approaches when writing code in a hierarchical style called **Top-Down** and **Bottom-Up** methodology. Typically, designers use these two approaches side-by-side to construct complex circuits.

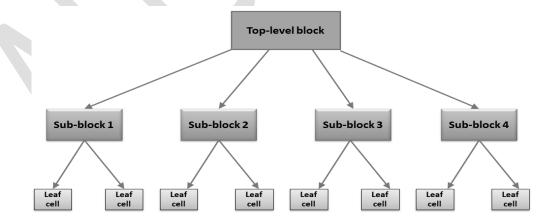

### 1. Top-Down Methodology

In a top-down design methodology, we define the top-level block and identify the subblocks necessary to build the top-level block. We further subdivide the sub-blocks until we come to leaf cells, which are the cells that cannot further be divided.

Figure: Block representation of **Top-Down** methodology

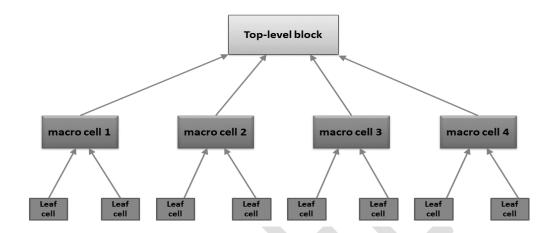

#### 2. Bottom-Up Methodology

In a bottom-up design methodology, we first identify the building blocks that are available to us. We build bigger cells, using these building blocks. These cells are then used for higher-level blocks until we build the top-level block in the design.

Figure: Block representation of **Bottom-Up** methodology

# Example 07

The following example demonstrates the Verilog HDL code of a full adder following the **Hierarchical Modeling** style. In the design, the half adder is constructed from the predefined logic gates and then the half adder instance is used twice to design the full adder. This creates two instances in the same module.

```

module Full_Adder(A,B,Cin,sum,carry); // Top module

input A,B,Cin;

output sum, carry;

wire s1,c1,c2;

Half Adder sm1(s1,c1,A,B);

Half_Adder sm2(sum,c2,s1,Cin);

or o1(carry,c1,c2);

endmodule

8

module Half_Adder(s,c,x,y); // macro cell

10

11

input x,y;

12

output s,c;

xor s1(s,x,y); // predefined primitive or leaf cells

13

14

and c1(c,x,y);

15

endmodule

```

**N.B.** One module can be instantiated to another module without maintaining the I/O sequence using the Name Wise Instantiation or Explicit method (.Exact\_Port(Port\_to\_be\_Assigned)).

# **Blocking and Non-Blocking Assignment**

Blocking (=) and non-blocking (<=) assignments are provided to control the execution order within an always block. All the previous examples of combinational circuits used blocking assignments. But if the subsequent assignments depend on the results of preceding assignments non-blocking assignments needed to be used. The following examples demonstrates the use of blocking and non blocking assignments.

#### Example 08

In the following example, we have tried to design a shift register module named **shift\_reg** using the blocking assignment.

```

module shift reg(clock, W,Q);

input clock,W;

2

output reg[3:0]Q;

always@(posedge clock)

5

begin

6

Q[3]=w;

7

Q[2]=Q[3];

8

Q[1]=Q[2];

9

Q[0]=Q[1];

10

end

endmodule

```

Now let us try to realize the output of Example 07 for that let us consider Initially Q=0000 and W=1. Now for the first two positive edges of the clock, the output will be following.

```

Output

//After the first positive edge of the clock

Q[3]=W=1;

Q[2]=Q[3]=1;

Q[1]=Q[2]=1;

Q[0]=Q[1]=1;

//After the second positive edge of the clock

Q[3]=W=1;

Q[2]=Q[3]=1;

Q[1]=Q[2]=1;

Q[0]=Q[1]=1;

```

Now from the output, we can notice that the output is always the same. For a shift registrar, we know that the output will propagate bit-wise sensing each clock trigger but in the design of Example 08 that is absent due to the use of blocking assignment as the variable update is executed in the order they are coded. It should be noted that the blocking assignment blocks the

execution of the next statement till the current statement is executed. So, it can be said that blocking assignment is useful for combinational circuits.

#### Example 09

In the following example, we have modified the **shift\_reg** module of Example 08 by replacing the **blocking** assignment with "**non-blocking**".

```

module shift reg(clock, W,Q);

input clock,W;

output reg[3:0]Q;

always@(posedge clock)

begin

6

Q[3] <= w;

7

Q[2] <= Q[3];

8

Q[1] <= Q[2];

9

Q[0] <= Q[1];

10

end

endmodule

11

```

Now let us try to realize the output of Example 08 for that let us consider Initially Q=0000 and W=1. Now for the first two positive edges of the clock, the output will be following.

```

Output

//After the first positive edge of the clock

Q[3]=W=1

Q[2]=Q[3]=0

Q[1]=Q[2]=0

Q[0]=Q[1]=0

//After the second positive edge of the clock

Q[3]=W=0

Q[2]=Q[3]=1

Q[1]=Q[2]=0

Q[0]=Q[1]=0

```

Now from the output, we can notice that the output is propagating bit-wise by sensing each clock trigger after using the blocking assignment as the variable update process is executed in parallel. In this code execution of the next statement is not blocked due to the execution of the current statement. This method is useful for modeling sequential circuits and generating concurrent statements.

There are three types of assignments in Verilog, **continuous** (assign), **blocking** (=), and **non blocking** (<=).

The following example demonstrates the Verilog HDL code of a D Latch

```

module D_FF(clock,D,Q);

input clock,D;

output reg Q;

always@(*)

if(clock)

Q<=D;

endmodule

```

#### **Example 11**

The following example demonstrates the Verilog HDL code of a D flip-flop. A D flip-flop is a 1-bit data storage device that saves one-bit data depending on its input D and clock pulse. When a clock edge is triggered, whatever input is present in D goes to the output Q.

```

module D_FF(clock,D,Q);

input clock,D;

output reg Q;

always@(posedge clock)

Q<=D;

endmodule

```

# Example 12

The following example demonstrates the Verilog HDL code of a 4 to 2 priority encoder with a valid bit. In the example, the **casex** statement is used. In Verilog, there are three types of variations in case. The **case**, **casex** and **casez** all do bit-wise comparisons between the selecting *case expression* and individual case item statements. In the **case** statement, the values **x** or **z** in an alternative are checked for an exact match with the same values in the controlling expression. On the other hand, **casex** ignores any bit position containing an 'x' or 'z'. The **casez** statement only ignores bit positions with a 'z'.

```

1

module p_encoder_4to2(D,Y,V);

//declaring variable for input

2

input [3:0]D;

output reg [1:0]Y; //declaring variable for output

//declaring the variable for valid bit

output reg V;

always@ *

5

begin

7

casex(D)

8

4'b0001:

9

begin

10

Y=2'b00; V=1;

11

end

```

```

4'b001x:

12

13

begin

14

Y=2'b01; V=1;

15

end

4'b01xx:

16

begin

17

18

Y=2'b10; V=1;

19

end

20

4'b1xxx:

begin

21

Y=2'b11; V=1;

22

23

end

24

default:

25

begin

Y=2'bx; V=0;

26

27

end

28

endcase

29

end

30 endmodule

```

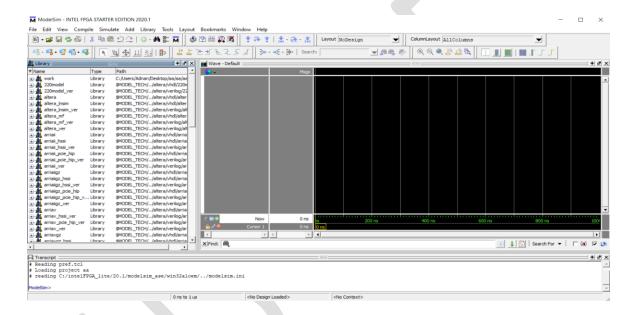

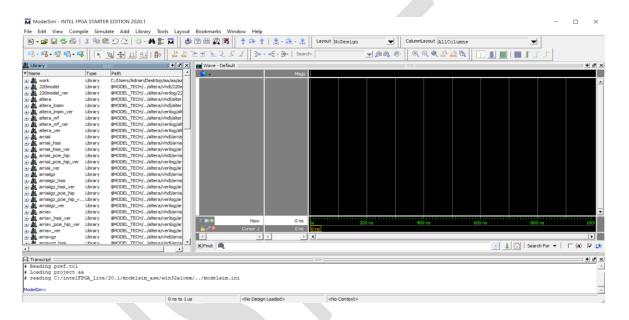

# Simulating Verilog HDL

1. Find the following icon on your PC and double-click on the icon to run the software. (Search: ModelSim - Intel FPGA Starter Edition Model Technology ModelSim - Intel FPGA Edition vsim 2020.1 (Quartus Prime 20.1))

2. The following window will pop up.

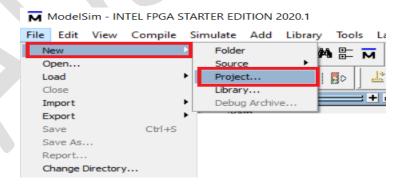

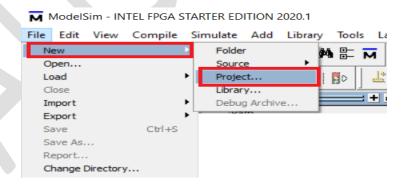

3. Execute File → New → Project. The Create Project window will appear.

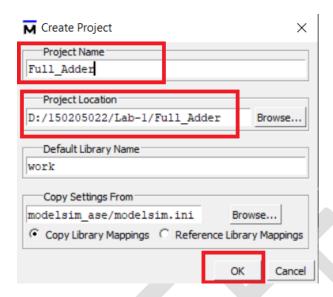

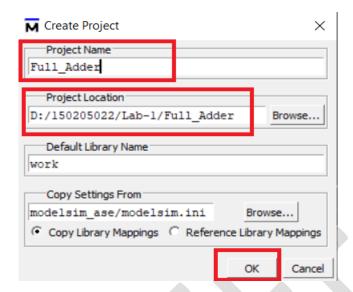

4. In the **Create Project** window change the **Project Location** to your directory (e.g. D:/150205022/Lab-1/Full\_Adder) and give a name in the **Project Name** field. After that click on the **OK** button.

[Project name must be same as the top module]

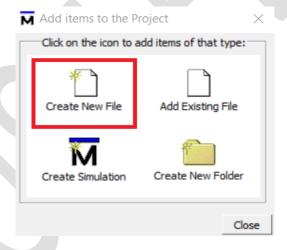

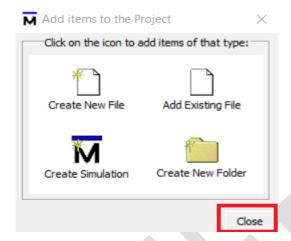

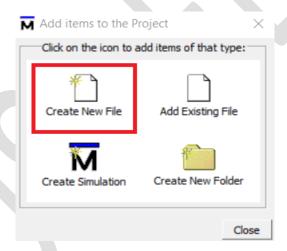

5. The Add items to the Project window will appear. Select the Crete New File button.

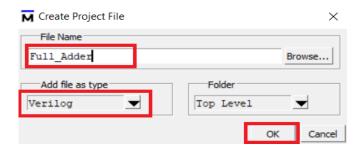

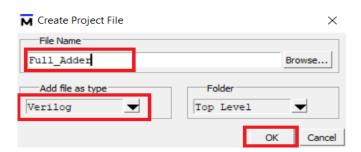

6. In the **Create Project File** window fill up the **File Name** field which must be identical to the project name and top module name. Also, select Verilog from the **Add file as type** dropdown menu. And ten click **OK** button.

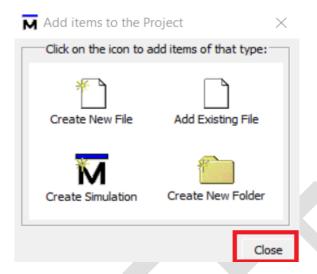

7. The **Add items to the Project** window will appear again. Click on the **Close** button.

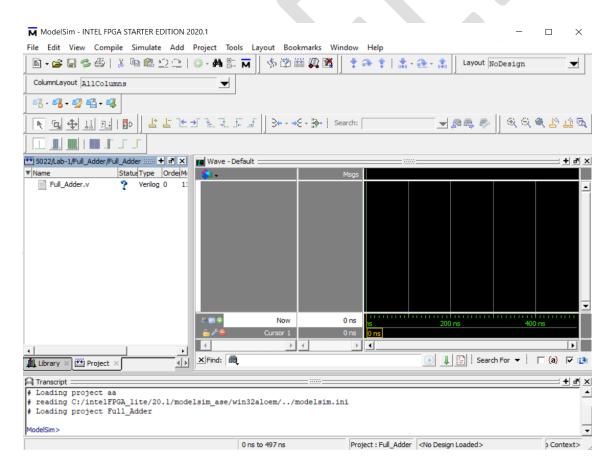

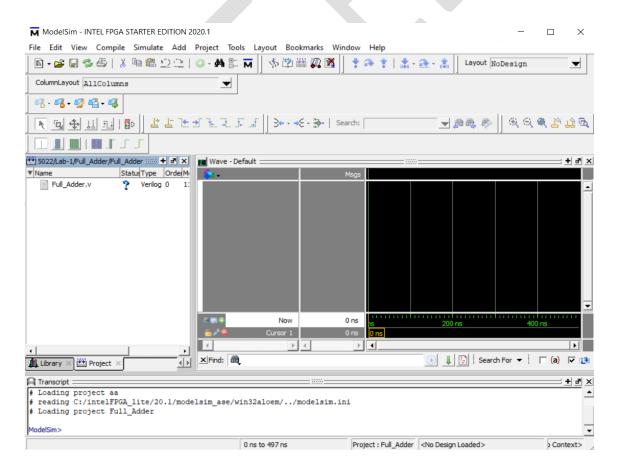

8. Now the ModelSim window will look like the following figure.

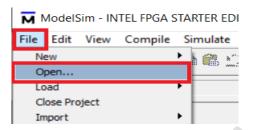

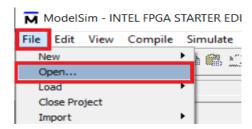

9. Now to open the editor window execute File → Open...

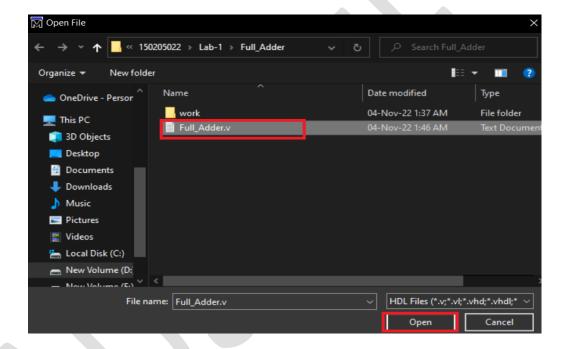

10. From the appeared file browser select your Verilog file(.v format)

11. In the editor window write the Verilog module of your design. And save using the shortcut executing **Ctrl+S** every time.

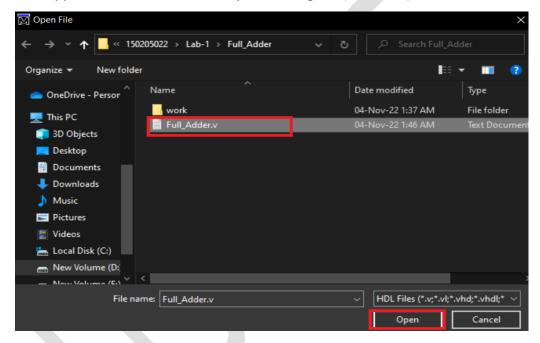

12. Now click on the **Compile All** icon for compiling the design.

[alternatively, execute Compile → Compile All ]

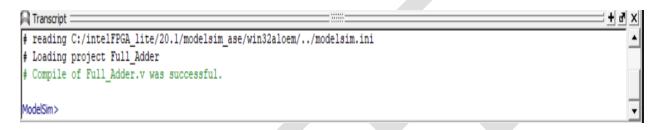

13. After successful compilation you will get the following message will appear in the **Transcript** window.

14. Now to simulate the design click on the **Simulate** icon.

[alternatively, execute Simulate→ Start Simulation.. ]

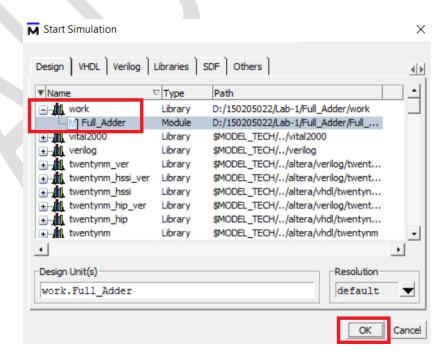

15. The **Start Simulation** window will appear. From the **Design** tab, execute **work** → **<click on your project module name>** and click on the **OK** button.

16. The following message will appear in the transcript if everything is done correctly.

```

ModelSim> vsim -gui work.Full_Adder

# vsim -gui work.Full_Adder

# Start time: 04:03:27 on Nov 04,2022

# Loading work.Full_Adder

```

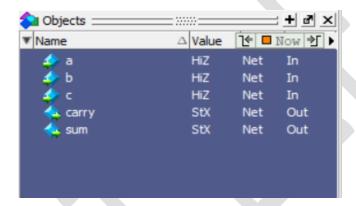

17. The input and output variables defined in the Verilog will appear in the **Objects** window.

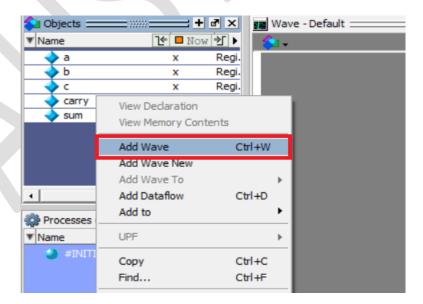

18. Now go to the **Wave** window and select all the input and output variables of the **Objects** window and by right-clicking on your mouse execute **Add Wave** to place them in the **Wave** window.

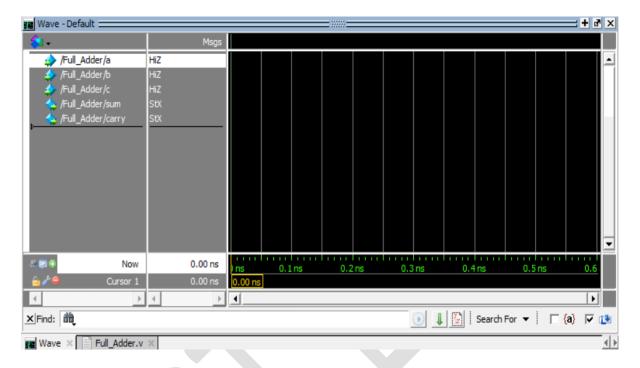

19. All the input and output variables will be placed on the **wave** window and the wave window will look like the following.

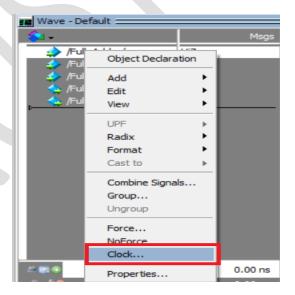

20. Now apply clock to each input variable. Right-clicking any input variable and from the popped-up menu execute **Modify** → **Clock**.

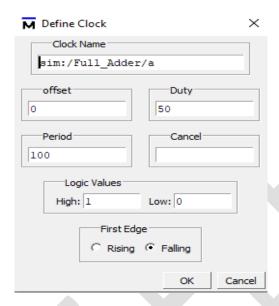

21. The **Define Clock** window will appear. Set parameters as per your requirement keep in mind all the units are in picoseconds by default.

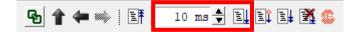

22. After defining all the input clocks, to evaluate the outputs write **run 100 ps** on the **Transcript** of ModelSim. Then the simulation will be performed for 100 ps.

Alternatively, we can run the wave output using the Run icon by typing the Run length

[Give run length according to your requirement.]

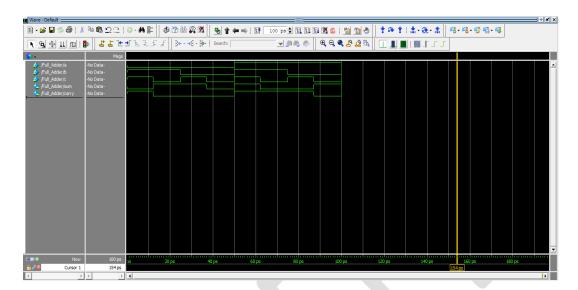

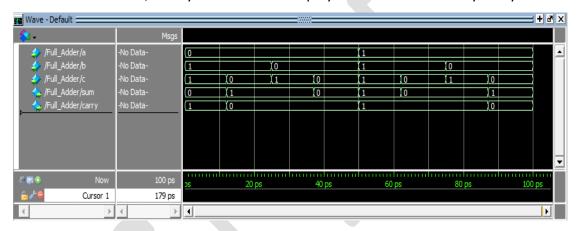

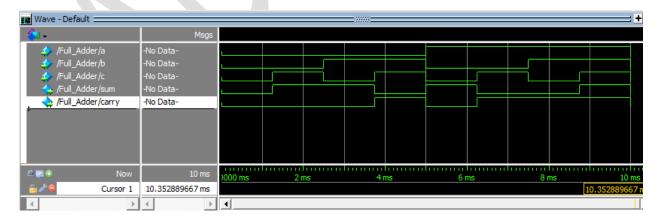

23. The wave window will look like the following figure after simulation.

If you need to change the clock pulse you must reset all the clocks before changing clocks otherwise the inputs and outputs will change after the previous run time which is not a convenient way to represent the inputs and outputs. The command "restart" is used in the transcript for resetting all the clock. Alternatively, restart can be performed by executing Simulate -> Restart

# **Showing Binary values on the Wave**

Sometimes it is hard to verify the functionality of a digital system from the wave. For easy functional verification, we can read the binary values from the wave of ModelSim by doing the following steps.

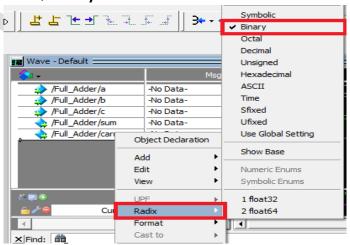

Select all the input and output variables on the clock and right-click on the mouse and execute Radix → Binary.

II. After changing the **Radix**, change the **Format** type similarly by selecting all input and output variables on the wave by right-clicking on the mouse and then executing **Format** → **Literal**.

III. Now on the wave, binary values will be displayed which can be easily analyzed.

# **Changing Clock Unit**

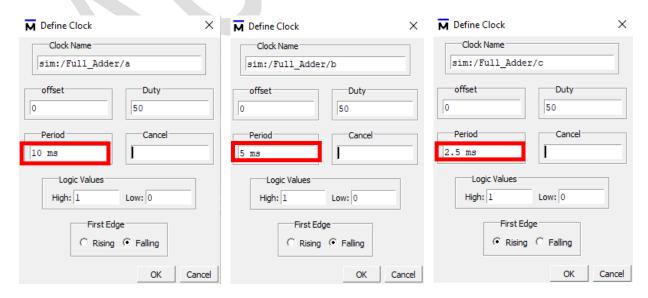

In step 21 it is mentioned that ModelSim's default timing unit is picosecond. But in some cases, we may need to define clocks in other units. Let us consider, that we need to define the period of a, b, and c as 10ms, 5ms, and 2.5ms respectively. Now define the clock a, b, and c as shown in the below figures.

Page 29 of 129

To view output for all the input combinations the run length should be equal to the maximum period.

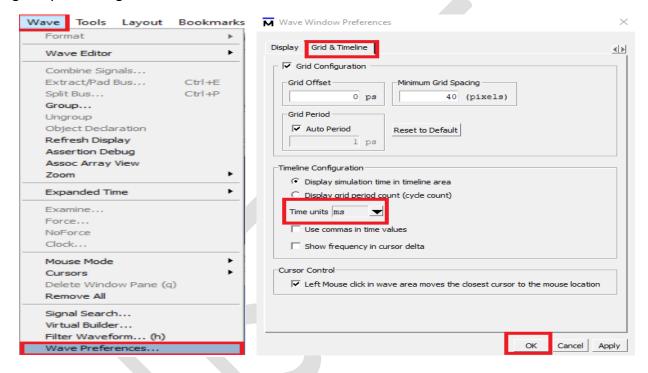

As all the units are in milliseconds, for easy visualization we can change the time units of the wave grid by executing  $\mathbf{Wave} \rightarrow \mathbf{Wave}$  Preferences  $\rightarrow$  Grid & Timeline  $\rightarrow$  Time units  $\rightarrow$  ms.

Now the ModelSim wave window will look like the following figure.

Similarly, for femtoseconds, nanoseconds, and microseconds, we can use **fs**, **ns**, and **ms** respectively

# **Post Lab Tasks**

- 1. Test the functionality of each example (4-12) using the ModelSim wave.

- 2. Design three input NOR gate using the switch level abstraction.

- 3. Design a 4-bit Carry Look Ahead adder using the concept of hierarchical modeling.

- 4. Design a BCD adder using the behavioural modeling technique.

# Lab-2: Introduction to Functional Verification Using Verilog Testbench.

# **Objective**

The main objectives of this lab are:

- Familiarization with test bench module.

- Learning different techniques for generating test vectors

- Verifying combinational circuits imposing test vectors.

#### Introduction

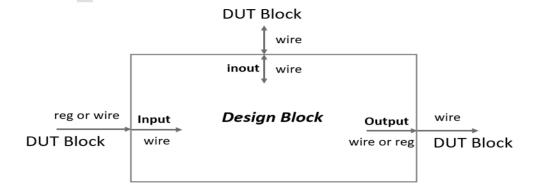

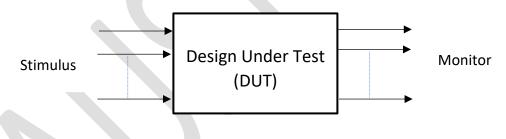

The test bench is an automated way of verifying and validating a digital design. A test bench is a procedural block that executes only once. Particularly the "initial" procedural block is used for the test bench. Only for repeated clock generation, the "always" procedural block is used. Test bench generates clock, reset, and the required test vectors for a given design under test (DUT) and hence by monitoring the output functionality of the design is verified. During synthesizing a design, a test bench is not required it is required during simulation only.

Block of Design Under Test

#### **Rules of Testbench**

- I. Define timescale using the command " `timescale <unit>/<precision> ".

- II. Instantiate the top module in the test bench module.

- III. Declare the input and output of design as "reg" and "wire" type respectively in the test bench module.

- IV. Specify the test vectors for different delays using the command "#<time\_delaye>".

- V. Use "\$display()" or "\$monitor()" commands to show outputs for the given test vectors in the transcript.

- VI. The "initial" procedural block must be declared at least once.

- VII. Terminate testbench using the command "\$finish".

- VIII. Monitor the outputs for functional verification using the transcript and wave.

The following example demonstrates the Verilog HDL code of a half adder.

```

module Half_Adder(s,c,x,y);

input x,y;

output s,c;

assign s=x^y;

assign c=x&y;

endmodule

```

The following Verilog HDL code demonstrates the **Testbench Module** of the half adder of Example 01 for random test inputs.

```

1

`timescale 1ns/1ps

module HA_TB;

3

reg a,b;

wire s,c;

Half_Adder Ha_dut(s,c,a,b);

initial

begin

7

8

#0 a=0; b=0;

9

#5 a=0; b=1;

10

#5 a=1; b=0;

#5 a=1; b=1;

11

#5 $finish;

12

13

end

endmodule

14

```

The previous **Testbench Module** of half adder can only generate test vectors for a certain interval but not periodic. The following **Testbench Module** of half adder. The forever loop-like procedural block **"always"** is used to generate periodic inputs.

```

1

`timescale 1ns/1ps

module HA_TB;

reg a,b;

wire s,c;

Half_Adder Ha_dut(s,c,a,b);

Initial

7

begin

8

a=0; b=0;

end

10

always

#10 a=~a; // for time period 20 ns

11

12

always

13

#5 b=~b;

// for time period 10 ns

14

initial

15

#20 $finish;

15 endmodule

```

The following example demonstrates the Verilog HDL code of a full adder.

```

1

module Full_Adder(A,B,Cin,sum,carry);

2

input A,B,Cin;

output sum, carry;

4

wire s1,c1,c2;

Half_Adder sm1(s1,c1,A,B);

Half_Adder sm2(sum,c2,s1,Cin);

or o1(carry,c1,c2);

endmodule

9

module Half Adder(s,c,x,y);

10

input x,y;

11

output s,c;

12

assign s=x^y;

13

assign c=x&y;

endmodule

14

```

The following Verilog HDL code demonstrates the **Testbench Module** of the full adder of Example 02 for random test inputs.

```

`timescale 1ns/100ps

1

module Full_Adder_TB;

2

3

reg a,b,c;

wire sum, carry;

Full_Adder FA_DUT(a,b,c,sum,carry);

initial

7

begin

8

$monitor($time, " a=%b, b=%b, c=%b, sum=%b, carry=%b", a ,b, c, sum, carry);

9

#0 a=0; b=0; c=1;

10

#5 b=1;

#5 a=1; b=1; c=1;

11

12

#5 $finish;

13

end

14

endmodule

```

# Example 03

The following example demonstrates the Verilog HDL code of a 2 to 4 decoder.

```

module decoder_2to4(s,e,y);

2

input [1:0] s;

3

input e;

output reg [3:0]y;

integer k;

5

always@ (s,e)

7

begin

8

for (k=0;k<=3;k=k+1)

9

begin

if ((s==k) \&\& (e==1))

10

y[k]=1;

11

12

else

13

y[k]=0;

14

end

end

15

endmodule

16

```

The following Verilog HDL code demonstrates the **Testbench Module** of the 2 to 4 decoder of Example 03.

```

`timescale 1ns/1ps

1

2

module decoder_2to4_TB;

reg [1:0]s; reg e;

wire [3:0]y;

5

decoder_2to4 dut(s,e,y);

6

initial

7

begin

8

$monitor($time, " e=%b, s=%b, y=%b", e ,s, y);

9

e=0;

#5 e=1; s=2'b00;

10

#5 s=2'b01;

11

12

#5 s=2'b10;

#5 s=2'b11;

13

#5 s=2'b00;

14

#5 s=2'b01;

15

#5 s=2'b10;

16

17

#5 s=2'b11;

18

#5 $finish;

19

end

endmodule

20

```

The following Verilog HDL code demonstrates another **Testbench** Module to verify the 2 to 4 decoder of Example 03 which is efficient than the previous one.

```

`timescale 1ns/1ps

module decoder 2to4 TB;

reg [1:0]s; reg e;

wire [3:0]y;

integer i,j;

decoder 2to4 dut2(s,e,y);

initial

8

begin

9

e=0:

10

$monitor($time, "e=%b, s=%b, y=%b", e ,s, y);

11

for (j=1;j<=2;j=j+1)

12

begin

13

for (i=2'b00;i<=2'b11;i=i+1)

14

begin

15

#5 e=1; s=i;

16

end

17

end

#5 $finish;

18

19

end

20

endmodule

```

# Example 04

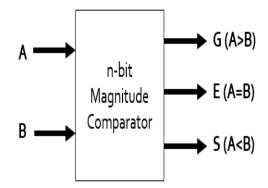

A magnitude comparator is a combinational circuit that compares the magnitude of two n-bit numbers A and B. The comparison of two numbers is an operation that determines whether one number is greater than, less than, or equal to the other number. The outcome of the comparison is specified by three binary variables G, E, and S that indicate whether A>B, A=B, and A<B respectively. In a magnitude comparator at a time, only one output variable can be logically high.

Block diagram of a magnitude comparator

The following example demonstrates the Verilog HDL code of a 2-bit magnitude comparator. The module has 2 inputs A and B each are 2-bit numbers When.

```

A>B outputs G=1, E=0, S=0

A=B outputs G=0, E=1, S=0

A<B outputs G=0, E=0, S=1

```

```

1

module mag_comp_2bit(A,B,G,E,S);

2

input [1:0]A,B;

// declaring 2-bit input variables A and B

3

output reg G,E,S;

4

always@*

// * symbol means the sensitivity list will be detected automatically

5

begin

6

if (A>B)

7

begin

8

G=1'b1;

9

E=1'b0;

S=1'b0;

10

11

end

12

else if (A==B)

13

begin

14

G=1'b0;

15

E=1'b1;

16

S=1'b0;

17

end

18

else

19

begin

20

G=1'b0;

21

E=1'b0;

22

S=1'b1;

23

end

24

end

25

endmodule

```

The following Verilog HDL code demonstrates another Testbench module to verify the 2-bit magnitude comparator of Example 04.

```

`timescale 1ns/1ps

module mag_comp_2bit_TB;

reg [1:0]A,B;

wire G,E,S;

integer i,j;

mag_comp_2bit dut(A,B,G,E,S);

initial

8

begin

$monitor($time, "A=%b, B=%b, G=%b, E=%b, S=%b", A, B, G, E, S);

9

10

for (j=2'b00;j<=2'b11;j=j+1)

begin

11

12

A=j;

13

for (i=2'b00;i<=2'b11;i=i+1)

14

begin

#5 B=i;

15

16

end

17

end

18

#0 $finish;

19

end

20

endmodule

```

# **Example 05**

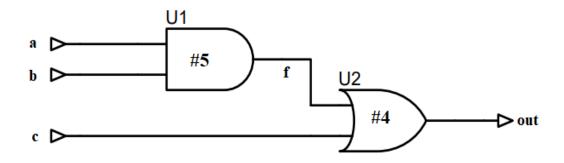

The following example demonstrates the Verilog HDL code of delayed gates

```

1    `timescale 1ns/1ps

2    module delay_gate(a,b,c,f,out);

3    input a,b,c;

4    output out,f;

5    and #(5) U1(f,a,b);

6    or #(4) U2(out,f,c);

7    endmodule

```

The following Verilog HDL code demonstrates another Testbench module to verify the logic arrangement shown in Example 05.

```

`timescale 1ns/1ps

module delay_gate_TB;

reg a,b,c;

wire out,f;

delay_gate dut(a,b,c,f,out);

initial

7

begin

8

a=1'b0; b=1'b0; c=1'b0;

9

#10 a=1'b1; b=1'b1; c=1'b1;

#10 a=1'b1; b=1'b0; c=1'b0;

10

#20 $finish;

11

12

end

endmodule

13

```

# **Simulating Testbench**

1. Find the following icon on your PC and double-click on the icon to run the software. (ModelSim - Intel FPGA Starter Edition Model Technology ModelSim - Intel FPGA Edition vsim 2020.1 (Quartus Prime 20.1))

2. The following window will pop up.

3. Execute File → New → Project. The Create Project window will appear.

4. In the **Create Project** window change the **Project Location** to your directory (e.g. D:/150205022/Lab-1/Full\_Adder) and give a name in the **Project Name** field. After that click on the **OK** button.

[Project name must be same as the top module]

5. The **Add items to the Project** window will appear. Select the **Crete New File** button.

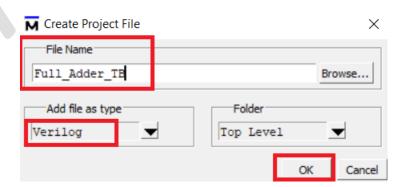

6. In the **Create Project File** window fill up the **File Name** field which must be identical to the project name and top module name. Also, select Verilog from the **Add file as type** dropdown menu. And then click the **OK** button.

7. The **Add items to the Project** window will appear again. Click on the **Close** button.

8. Now the ModelSim window will look like the following figure.

8. Now to open the editor window execute File -> Open...

9. From the appeared file browser select your Verilog file (.v format)

10. In the editor window write the Verilog module of your design. And save using the shortcut executing **Ctrl+S** every time.

```

D:/AUST Teaching/4232/VLSI-2 Verilog codes/VLSI -II_Lab-2/E2 Full_Adder/Full_Adder.v - Default :

Ln#

module Full Adder (A, B, Cin, sum, carry);

1

2

input A, B, Cin;

3

output sum, carry;

4

wire sl,cl,c2;

5

Half Adder sml(sl,cl,A,B);

6

Half Adder sm2(sum,c2,s1,Cin);

7

or ol(carry,cl,c2);

8

endmodule

9

module Half Adder(s,c,x,y);

10

input x, y;

11

output s,c;

12

assign s=x^y;

13

Lassign c=x&y;

14

endmodule

```

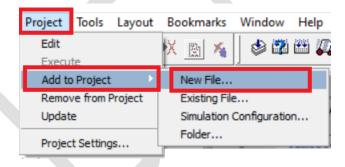

11. Now click on the Compile All icon for compiling the design.

[alternatively, execute Compile → Compile All ]

12. After successful compilation you will get the following message will appear in the **Transcript** window.

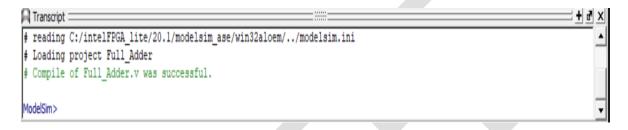

13. Now, to write the test bench code create a new Verilog file at first click on the project window then execute **Project → Add to Project → New File...**

14. Now in the **Create Project File** window, fill up the **File Name** field which will be our test bench module name. Also, select **Verilog** from the **Add file as type** dropdown menu. And then click the **OK** button.

15. Now there will be two files under the project.

16. Open the testbench file following step 10 and write the testbench code in the editor.

```

D:/150205022/Full_Adder/Full_Adder_TB.v (/Full_Adder_TB) - Default *:

Ln#

1

`timescale lns/100ps

2

module Full Adder TB;

3

reg a,b,c;

4

wire sum, carry;

5

Full Adder FA DUT(a,b,c,sum,carry);

6

initial

7

□ begin

8

$monitor($time, " a=\frac{2}{2}b, b=\frac{2}{2}b, sum=\frac{2}{2}b, carry=\frac{2}{2}b", a ,b, c, sum, carry);

9

#0 a=0; b=0; c=1;

10

#5 b=1;

11

#5 a=0; b=1; c=1;

12

#5 $finish;

13

end

14

endmodule

```

17. Now click on the **Compile All** icon for compiling the design.

[alternatively, execute Compile → Compile All ]

18. Now to simulate the design click on the **Simulate** icon.

[alternatively, execute Simulate→ Start Simulation.. ]

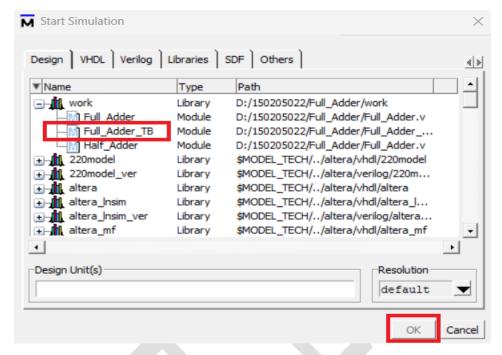

19. The **Start Simulation** window will appear. From the **Design** tab execute **work** → **<click on your test bench module>** and click on the **OK** button.

20. The following message will appear in the transcript if everything is done correctly.

```

# End time: 03:44:35 on Nov 04,2022, Elapsed time: 0:04:38

# Errors: 0, Warnings: 2

# vsim -gui work.Full_Adder_TB

# Start time: 03:44:35 on Nov 04,2022

# Loading work.Full_Adder_TB

# Loading work.Full_Adder_TB

# Loading work.Full_Adder_TB

```

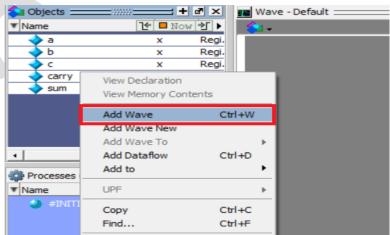

21. Graphically the functionality of the design can be checked from the wave window of the ModelSim Simulator. Execute view → wave if it doesn't appear automatically. Now go to the Wave window and select all the input and output variables of the Objects window and by right-clicking on your mouse execute Add Wave to place them in the Wave window.

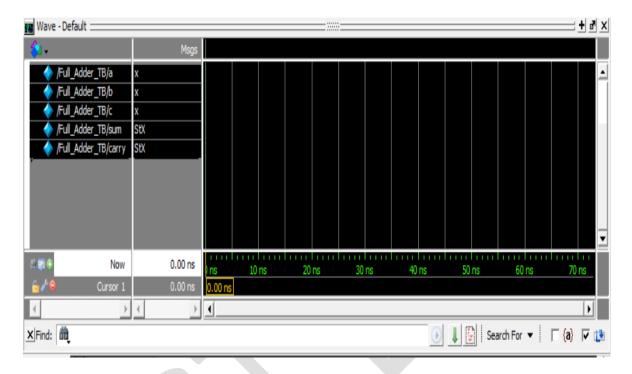

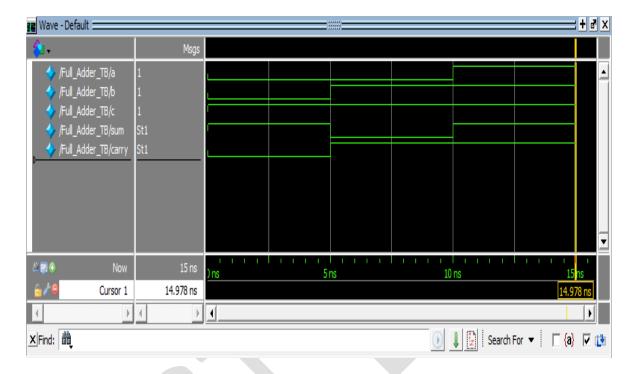

22. All the input and output variables will be placed on the **wave** window and the wave window will look like the following figure.

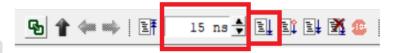

23. Now to evaluate the outputs write **run 15 ns** on the Transcript of ModelSim. Alternatively, we can run the wave output using the **Run** icon by typing the **Run length.**

[Give run length according to your requirement.]

24. The **Finish Vsim** window will appear. Click **No** otherwise the ModelsSim will be closed immediately.

25. Now for the given test vectors the functionality of the design can be verified from the wave output generated by the **ModelSim** simulator.

26. Functionality of the design can also be verified from the transcript generated by the **ModelSim** simulator. Execute **view** → **Transcript** if it doesn't appear automatically.

## **Post Lab Tasks**

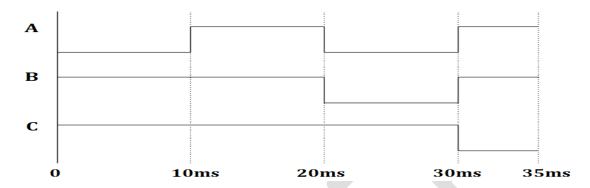

1. Write a testbench program to test a full adder circuit with the signal shown below.

- 2. Differentiate between

- a. **\$finish** and **\$stop** command.

- b. **\$monitor** and **\$display** command.

- 3. Is it possible to check the functionality of a sequential circuit from the transcript only?

- 4. Can we use the "always" procedural block in the Testbench module?

- 5. Is it possible to generate periodic stimuli in the testbench? If possible, generate the signals of task-1 for two periods.

# Lab-3: Modeling Sequential Systems and Finite State Machine Using Verilog HDL

# **Objective**

The main objectives of this lab are:

- Functional verification of sequential circuits using Verilog Testbench.

- Modeling finite state machine and its functional verification using Verilog Testbench.

#### Introduction

A digital system can be either in the form of combinational logic or sequential logic. In combinational logic, the output of a circuit depends only on the presently applied inputs. On the other hand, the output of a sequential circuit depends on the applied input and the present states. Most practical digital systems are sequential. To design a digital system, the behavioral abstraction is used as a reference to create and refine a synthesizable register transfer level (RTL) abstraction that captures the desired functionality required by the design specification.

## Example 01

Flip-flops are the building blocks of sequential circuits. In the following example, the Verilog HDL code of a positive edge-triggered T flip-flop with reset is demonstrated.

```

module T_FF(T,clk,reset,Q);

input T,clk,reset;

output reg Q;

always@(posedge clk)

begin

if(reset==0)

7

begin

8

if (T)

9

Q<=~Q;

10

else

11

Q \le Q;

12

end

13

else

14

Q \le 0;

15

end

16

endmodule

```

# **Testbench Module of Example 01**

The following Verilog HDL code demonstrates the **Testbench Module** of the T flip-flop of Example 01.

```

1

`timescale 1ns/1ps

2

module T_FF_TB;

reg T,clk,reset;

wire Q;

T_FF dut(T,clk,reset,Q);

initial

7

begin

8

T=0; clk=0; reset=1;

9

end

10

always

11

#2 clk=~clk;

12

initial

13

begin

#6 reset=0; T=1;

14

15

#4 reset=1; T=1;

16

#4 reset=1; T=0;

17

#2 reset=0; T=0;

#2 $finish;

18

19

end

20

endmodule

```

# Example 02

The following example demonstrates the Verilog HDL code of a positive edge-triggered JK flip-flop with clear.

```

module JK_FF(clk,J,K,Q,clear);

input clk,J,K,clear;

3

output reg Q;

always@ (posedge clk)

5

begin

if(clear==0)

6

7

begin

8

if (J==0 && K==0)

9

Q<=Q;

10

else if (J==0 && K==1)

11

Q<=0;

12

else if (J==1 && K==0)

13

Q<=1;

14

else

15

Q<=~Q;

16

end

17

else

18

Q=0;

19

end

endmodule

```

# **Testbench Module of Example 02**

The following Verilog HDL code demonstrates the **Testbench Module** of the JK flip-flop of Example 02.

```

`timescale 1ns/1ps

1

module JK_FF_TB;

3

reg clk,J,K,clear;

wire Q;

JK_FF JK_dut(clk,J,K,Q,clear);

6

initial

7

begin

8

clk=0; J=0; K=1;clear=0;

9

end

10

always

11

#2 clk=~clk;

12

initial

13

begin

14

#2 clear=1; J=1; K=0;

15

#4 clear=0; J=0; K=1;

16

#4 J=1;

17

#4 J=0;

18

#4 $finish;

19

End

20

endmodule

```

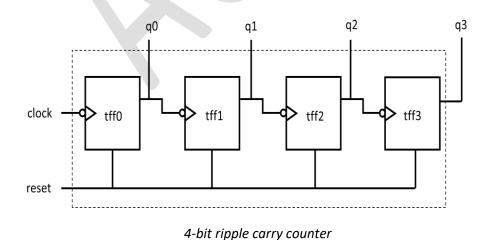

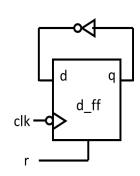

## Example 03

In this example a 4-bit ripple carry counter will be designed using the submodule of a T flip-flop and each T filp-flop is designed using leaf module of D flip-flop. The block representation of the ripple carry counter is shown below.

T flip flop using D flip flop

The following example demonstrates the Verilog HDL code of a 4-bit asynchronous ripple-carry country as shown in the following block diagram.

```

module rc_counter(q,clock,reset);

2

output [3:0] q;

input clock,reset;

t_ff tff0 (q[0], clock, reset);

t_ff tff1 (q[1], q[0], reset);

t_ff tff2 (q[2], q[1], reset);

t_ff tff3 (q[3], q[2], reset);

endmodule

10

module t_ff (q,clk,r);//T-Flip-Flop

output q;

11

input clk,r;

12

13

wire d;

14

d_ff dff1(q,d,clk,r);

15

not n1(d,q);

endmodule

16

17

module d ff (q,d,clk,r);//D-Flip-Flop

18

19

output reg q;

20

input d,clk,r;

always @(posedge r or negedge clk)

21

22

begin

23

if (r)

24

q<=1'b0;

25

else

26

q<=d;

27

end

28

endmodule

```

# **Testbench Module of Example 03**

The following Verilog HDL code demonstrates the **Testbench Module** of the 4-bit asynchronous ripple-carry counter of Example 03.

```

10

always

11

#5 clk=~clk;

12

initial

13

begin

$monitor($time, "clk=%b, res=%b, q=%b", clk, res, q);

14

15

res=1;

#15 res=0;

16

17

#180 res=1;

18

#10 res=0;

19

#20 $stop;

20

end

endmodule

21

```

#### Example 04

The following example demonstrates the Verilog HDL code of a simple 8-bit accumulator. The module is designed in such a way that when **reset=1** the output is set to 0 and when **reset=0** the output adds the input.

```

module accu(in, acc, clk, reset);

input [7:0] in;

input clk, reset;

output reg [7:0]acc;

always @(posedge clk)

begin

7

if (reset)

8

acc<=0;

9

else

10

acc<=acc+in;

11

end

12

endmodule

```

# **Testbench Module of Example 04**

The following Verilog HDL code demonstrates the **Testbench Module** of the accumulator of Example 04.

```

12 begin

#0 reset<=1; in<=1;

#5 reset<=0;

#50 $finish;

end

endmodule

```

#### **Example 05**

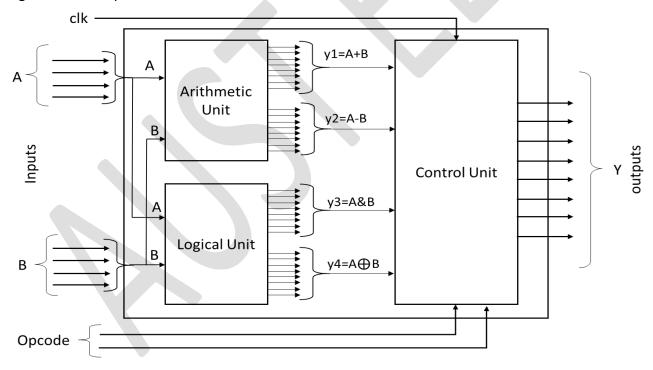

In this example, a 4-bit Arithmetic Logic Unit (ALU) shown in the following figure will be designed using Verilog HDL. The top module of the ALU is *alu\_4bit* and it is designed using three submodules: *logical\_unit*, *arithmetic\_unit*, and *control\_unit*. In the design, the two 4-bit inputs A and B are fed to the inputs of *arithmetic\_unit* and *logical\_unit* modules to perform two different arithmetic operations and two different logical operations according to the function table given below. Thus the *arithmetic\_unit* and *logical\_unit* generates four outputs y1,y2,y3, and y4 which are fed to the inputs of *control\_unit* module which generates the 8-bit output Y from the y1,y2,y3 and y4 depending on its 2-bit *Opcode* input. The output Y is also sensitive to the positive edge of the *clk* input.

The function table of the ALU is given below.

**Function Table**

| Opcode | Output (Y)     | Description of function |  |

|--------|----------------|-------------------------|--|

| 00     | A+B Add A to B |                         |  |

| 01     | A-B            | Subtract B from A       |  |

| 10     | A&B            | A&B Bitwise AND         |  |

| 11     | A⊕B            | Bitwise XOR             |  |

The following Verilog HDL code demonstrates the ALU mentioned in Example 05.

```

1

module alu_4bit(A,B,Y,clk,Opcode);

input [3:0]A,B;

3

input [1:0]Opcode;

input clk;

5

output [7:0]Y;

wire [7:0]y1,y2,y3,y4;

arithmetic_unit sm1(A,B,y1,y2);

logical_unit sm2(A,B,y3,y4);

control_unit sm3(y1,y2,y3,y4,clk,Opcode,Y);

endmodule

10

11

12

module arithmetic_unit(x,y,y1,y2);

13

input [3:0]x,y;

14

output reg[7:0]y1,y2;

15

always@(x,y)

16

begin

17

y1<=x+y;

18

y2<=x-y;

19

end

20

endmodule

21

22

module logical_unit(x,y,y3,y4);

23

input [3:0]x,y;

24

output [7:0]y3,y4;

25

assign y3=x&y;

26

assign y4=x^y;

27

endmodule

28

29

module control_unit(y1,y2,y3,y4,clk,Opcode,Y);

30

input [7:0]y1,y2,y3,y4;

31

input [1:0]Opcode;

32

input clk;

output reg[7:0]Y;

33

34

always@(posedge clk)

35

begin

36

if(Opcode == 2'b00)

37

Y<=y1;

else if(Opcode ==2'b01)

38

39

Y<=y2;

40

else if(Opcode ==2'b10)

41

Y<=y3;

42

else if(Opcode ==2'b11)

43

Y<=y4;

44

else

45

Y<=0;

46

end

endmodule

```

#### **Testbench Module of Example 05**

The following Verilog HDL code demonstrates the **Testbench Module** of the 4-bit ALU of Example 05.

```

`timescale 1ns/1ps

2

module alu_4bit_TB;

reg [3:0]A,B;

4

reg [1:0]Opcode;

5

reg clk;

wire [7:0]Y;

alu_4bit dut(A,B,Y,clk,Opcode);

7

initial

9

begin

10

clk = 1'b0; Opcode=2'b00; A=4'b0100; B=4'b1100;

11

end

12

always

13

#2.5 clk = ^clk;

14

initial

14

begin

#5 Opcode<=2'b01; A=4'b1000; B=4'b0111;

16

17

#5 Opcode<=2'b10; A=4'b1111; B=4'b1011;

#5 Opcode<=2'b11; A=4'b1001; B=4'b1010;

18

19

#5 $finish;

end

20

21

endmodule

```

# **Finite State Machine Design**

In a sequential circuit, outputs depend not only on the applied input values but also on the internal state. The internal state also changes with time. As the number of states in a sequential circuit is finite it is also referred to as a Finite State Machine (FSM). FSMs need memory to hold the current state and logic devices to determine the next state. Elevators(lift), vending machines, traffic signal systems, password generators etc. are examples of FSM.

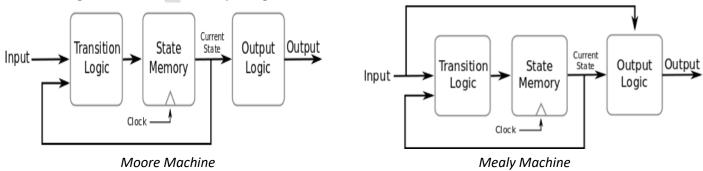

There are two types of finite state machines called the Mealy machine and the Moore Machine. In Mealy machines, the output is a function of the current state and inputs. In Moore machines, the output is a function of only the current state. To design FSMs, we need to find the state transition diagram or the state table.

FSMs are modeled in Verilog with an always block defining the state registers and combinational logic defining the next state and output logic.

# **Example 06**

In this example, the Verilog HDL code of a Mealy machine is demonstrated that generates output '1' when sequence 101 is detected in a bitstream.

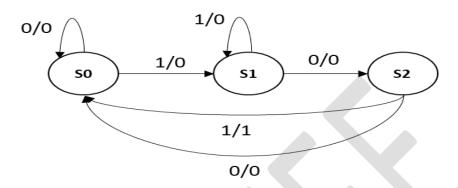

State Transition Diagram

The following Verilog HDL code demonstrates the sequence detector mentioned in Example 06.

```

module seq_101(i,clk,out);

1

2

input i,clk;

3

output reg out;

localparam S0=2'b00, S1=2'b01, S2=2'b10;

5

reg [1:0]state;

always@ (posedge clk)

7

begin

case (state)

9

S0: begin

10

out<=i?0:0;

11

state<=i?S1:S0;

12

end

S1: begin

13

14

out<=i?0:0;

15

state<=i?S1:S2;

16

end

17

S2: begin

18

out<=i?1:0;

19

state<=i?S0:S0;

20

end

21

default:

22

begin

23

out<=0;

24

state<=S0;

25

end

26

endcase

27

end

endmodule

28

```

# **Testbench Module of Example 06**

The following Verilog HDL code demonstrates the **Testbench Module** of the sequence detector of Example 06 where 0101001010-bit stream is generated.

```

`timescale 1ns/1ps

module seq_TB;

reg i,clk;

wire out;

seq_101 dut(i,clk,out);

initial

clk=0;

always

#2 clk=~clk;

9

10

initial

11

begin

12

#0 i=0;

13

#5 i=1; #4 i=0; #4 i=1; #4 i=0;

14

#4 i=0; #4 i=1; #4 i=0; #4 i=1;

15

#4 i=0;

#4 $finish;

16

17

end

18

endmodule

```

#### **Post Lab Tasks**

- 1. Design a negative edge triggered D flip flop with reset and verify its functionality using testbench.

- 2. In Example 06 how many 1s will be generated at the output if the input bitstream is 01010100? Verify your answer using testbench.

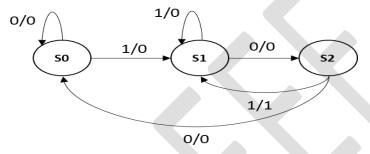

- 3. Write a Verilog program to implement the digital system represented by the following state transition diagram of a Mealy machine. Assume that system has input and output variables **in** and **Y**. The system functions when the positive edge of the clock is detected.

- 4. Design a Mealy machine to detect the 010 sequences hence verifying its functionality using testbench.

- 5. The state transition diagram of a two-bit counter is shown below. Assuming that each state changes when a positive edge clock is detected. Design and verify the system using Verilog HDL.

# Lab-4: Introduction to Unix Shell

# **Objective**

The main objectives of this lab are:

- Logging into the Cadence software installed Linux server.

- To get started with the Linux environment.

- To comprehend the file and directory management using shell command.

- To get familiar with Vim text editor.

#### Introduction

Electronic Device Automation (EDA) tools are required to run for a long time which consumes a huge amount of memory (RAM), runs in multiple threads/processes and are multiuser programs. For that, Unix or Linux is the ideal choice to run (EDA) tools.

In the upcoming lab classes, we will use different cadence tools preinstalled on the Linux server. For that, we have to login into your student account from the Windows operating system based computer allocated for the student use.

# **Steps to Login into Linux Server**

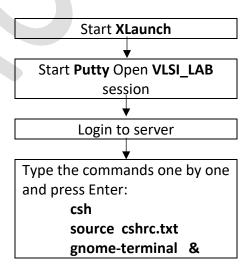

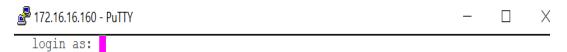

The following flowchart summarizes the steps to login into the Linux server.

#### The detailed instructions are given below

1. Find the Desktop shortcut icon for **XLaunch**. Double-click on it. Click **Next, Next, Next, Finish** (in that order) in the windows that pop up one after another.

After it starts, you will see the Xming icon at the bottom right corner of your Desktop screen.

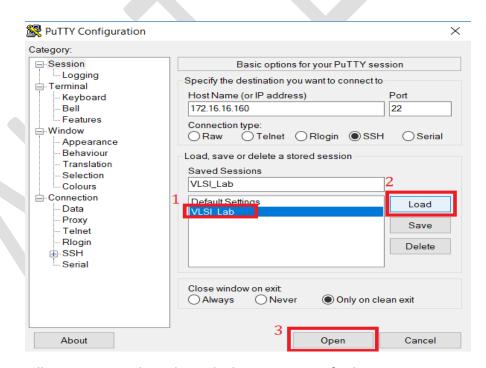

2. Find the icon for Putty. Double click on it to open it. 'Putty Configuration' window will pop-up

3. Select VLSI\_LAB under the 'Saved Sessions' category. Click Load and then click Open.

4. Now you will see a Terminal window which prompts you for login.

5. Log in to your workstation using your username and password. Your username will be eee\_<student id> and your password will be your student ID. When you are typing your password, the command window will not display the characters you type in, so make sure you are typing the right password. After logging in to your account, the terminal window should look like the following:

7. Then type **source cshrc.txt** and press the **'Enter'** key. The following message will be displayed in the Terminal window: Welcome to Cadence Tools That means you can use Cadence tools now.

8. Finally type **gnome-terminal &** and press the **'Ente**r' key to enter the Command Line Interface (CLI) of your account.

9. The Command Line Interface (CLI) of your account will look like the following screenshot.

#### **Lab Task**

The following flow chart summarizes the tasks to be performed in Lab-04.

# **Directory Management in Unix**

| Command | Description                                                                                   | Syntax                                  |

|---------|-----------------------------------------------------------------------------------------------|-----------------------------------------|

| pwd     | print name of current/working directory.                                                      | pwd                                     |

| ls      | lists directory contents.                                                                     | ls                                      |

| ls -ltr | lists directory contents by arranging them according to time by using the <b>-ltr</b> switch. | ls -ltr                                 |

| tree    | Show the file hierarchy inside a directory                                                    | tree                                    |

| mkdir   | make directories.                                                                             | mkdir <directory_name></directory_name> |

| cd      | Change directory.                                                                             | cd <directory_path></directory_path>    |

| cd ~/   | Goes to the home directory                                                                    | cd ~/                                   |

| cd ~    |                                                                                               | cd ~                                    |

| cd      | Goes to the previous directory.                                                               | cd                                      |

| cd/     |                                                                                               | cd/                                     |

| cd//    | Goes two directories back.                                                                    | cd//                                    |

# **Vim Editor in Unix**

| Command                     | Description                                           | Syntax                                       |  |

|-----------------------------|-------------------------------------------------------|----------------------------------------------|--|

| touch                       | Creates a file.(Extension can be .txt, .v, .tcl, etc) | n can be .txt, .v, .tcl, etc) touch test.txt |  |

| Press " i" or insert        | Enables the INSERT mode                               |                                              |  |

| :w                          | Writes/saves the text file.                           |                                              |  |

| :q                          | Quits from vim editor.                                |                                              |  |

| :wq                         | Writes the text and then quits the vim editor.        |                                              |  |

| :wq!                        | Forcefully writes and quits the vim editor through    |                                              |  |

|                             | bang(!)                                               | The commands of the                          |  |

| :set nu                     | Shows the line numbers.                               | vim editor can be                            |  |

| : <line no=""></line>       | The cursor moves to the specified line no.            | executed after                               |  |

| :set nu!                    | Removes the line numbers.                             |                                              |  |

| :/xyz                       | Used to search all the "xyz" in forward               |                                              |  |

|                             | (Use n to move from one to another)                   |                                              |  |

| :?xyz                       | Used to search all the "xyz" in backward              |                                              |  |

| :%s= <b>x</b> = <b>y</b> =g | Searches "x" and replaces with "y" globally           |                                              |  |

| u                           | Undo                                                  |                                              |  |

| Press Ctrl+R                | Redo                                                  |                                              |  |

# Reading and sourcing a file

| Command | Description                                | Syntax                         |

|---------|--------------------------------------------|--------------------------------|

| cat     | Checks the content inside a file.          | cat <file_name></file_name>    |

| source  | Reads and executes commands from the file. | source <file_name></file_name> |

| ./      |                                            | ./ <file_name></file_name>     |

# Files and directory manipulation in Unix

| Command | Description                                                                                                                             | Syntax                                                               |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| ср      | Copies files and directories.                                                                                                           | cp <source_file> <destination_file></destination_file></source_file> |

| rm      | Remove files.                                                                                                                           | rm <directory_name></directory_name>                                 |

| rmdir   | Removes empty directories.                                                                                                              | rmdir <directory_name></directory_name>                              |

| rm -rf  | Removes directories containing files by force recursive using force recursive switch.                                                   | rm -rf <directory_name></directory_name>                             |

| mv      | Moves one or more files and directories to a given location (if the location is not defined. it renames files on the current location). | mv <source_file> <destination_dir></destination_dir></source_file>   |

# **Other Useful Commands**

| Command/Key | Description                                                                   |

|-------------|-------------------------------------------------------------------------------|

| history     | Prints the previous commands executed in the bash terminal. (Syntax: history) |

| man         | Shows the documentation of any command (Syntax: man pwd)                      |

# **Shortcut Keys**

| Command/Key        | Description                                      |

|--------------------|--------------------------------------------------|

| Up/Down Arrow keys | Scrolls through command history.                 |

| Tab key            | Used to complete the command you are typing.     |

| Ctrl + Shift + C   | Copies the highlighted command to the clipboard. |

| Shift + Insert     | Pastes the contents of the clipboard.            |

| Ctrl + L           | Clears the terminal                              |

#### **Bash Script**

Bash scripts are typically used for handling directories and files, not for coding. But it can be useful for scripting with various arithmetic use cases and scenarios. Bash only supports integer arithmetic, so if we need to perform calculations with floating-point numbers, have to use separate utility in bash. There are several ways and syntax of performing arithmetic operations, using conditions and loops in bash. The below code is just a simple demonstration of arithmetic operations, *if..else..* statement, *for* loop and array declaration in bash. A bash script can be written using the vim editor and it should be saved with the extension *.sh*. The commands inside the script can be executed by sourcing the script.

```

a = 10

1

read -p "enter b:" b

#Stores user's input in b variable by prompting in display using -p

sum=$(($a+$b))

3

sub=$(($a-$b))

5

mult=$(($a*$b))

div=$(($a/$b))

echo "sum=$sum

$a-$b=$sub

$a*$b=$mult

$a/$b= $div"

10

11

if [$(($a%2)) == "0"]

#Using if..else.. statement to find whether a is even or odd

12

then

13

echo "$a is even"

14

else

15

echo "$a is odd"

16

17

c=($sum $sub $mult $div)

18

elements=${#c[@]}

#storing different variables in array c

#Counts the no of elements present in the array c

19

for((i=0;i < \$elements;i++))

20

#Using for loop to display all the elements present in array c

21

echo "${c[i]}"

22

done

```

#### **Post Lab Tasks**

- 1. How fractional values can be handled in bash?

- 2. Write a bash script to perform the following arithmetic operation.

$$y = \sin(5) + e^3 + \sqrt{3} + 2^3$$

- 3. Write a bash script that will show your root and home location whenever it is sourced.

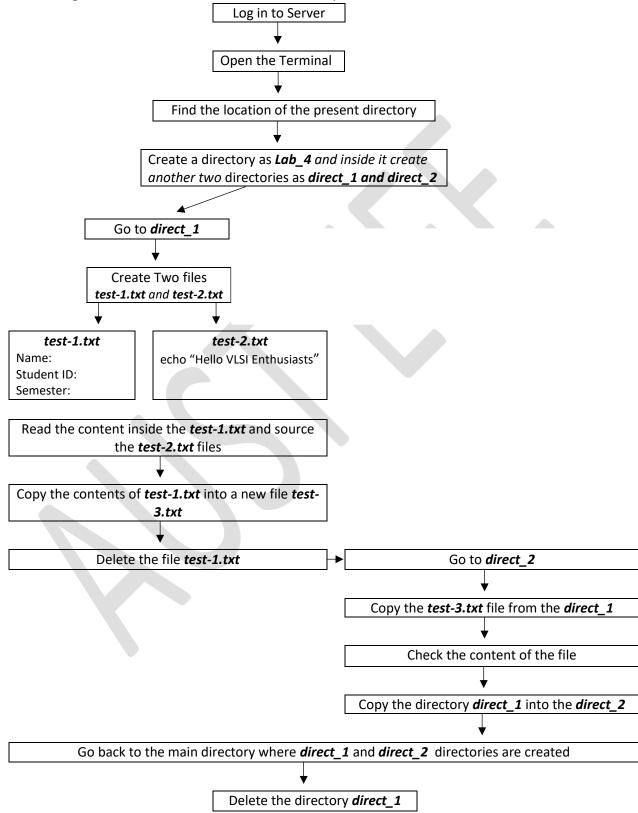

- 4. Write a bash script that will create the following hierarchy in your home.

# Lab-5: Synthesis using Genus Synthesis Solution

# **Objective**

The main objectives of this lab are:

- Familiarization with synthesis flow.

- Setting up synthesis constraints.

- Generating optimized gate-level netlist and Standard Design Constraints.

#### Introduction

Synthesis is a process of transforming RTL (a description of a circuit expressed in a language such as Verilog or VHDL written in behavioral modeling or data flow modeling) to technology-dependent or independent gate-level netlist including nets, sequential and combinational cells, and their connectivity. The main goal of synthesis are obtaining a gate-level netlist, logic optimization, inserting a clock-gating cell for power reduction, inserting DFT (Design for Testability) cell, and maintaining the logical equivalence between RTL and gate-level netlist. The best output of place and route depend on the synthesis.

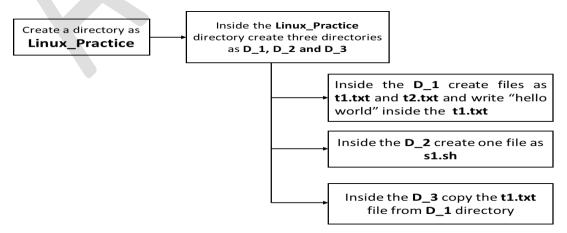

#### Synthesis = translation + optimization + mapping

Fig: Steps of Synthesis

Synthesis tools perform the following three steps to meet all the goals.

- Translation: Converts RTL into basic Boolean equation form which is technologyindependent representation.

- Optimization: Performs two types of optimizations.

- Logic optimization

- Detecting identical cell

- Optimize multiplexer

- Remove unused cell and net

- Reduced word size of the cell

#### Design optimization

- Reduced WNS (Worst Negative Slack) and TNS (Total Negative Slack)

- Power and area optimization

- Attempting to meet DRV (Design Rule Violation: Max Fanout, Max Transition, Max Capacitance)

- Mapping: Technology-independent Boolean logic equations are mapped to technologydependent library logic gates based on design constraints, and available gates in the technology library.

## Input and Output files of Physical Design

## Input Files

#### **Technology-Related Files**

- I. Technology file containing names, physical and electrical characteristics of metal layers, and design rules ( .lef )

- II. Timing and functionality information of the standard cell (.lib)

#### **Design Related Files**

- I. Post Synthesized or Gate Level Netlist (.v)

- II. Standard Design Constraints containing all timing and design limitations (.sdc)

#### Output Files

- I. Post-synthesized and optimized gate-level netlist (.v)

- II. Standard Design Constraints (.sdc)

#### **Lab Task**

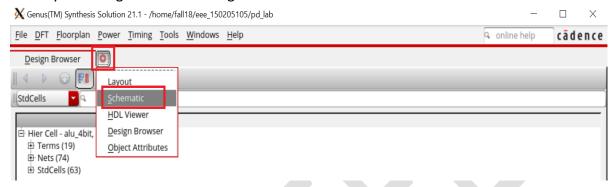

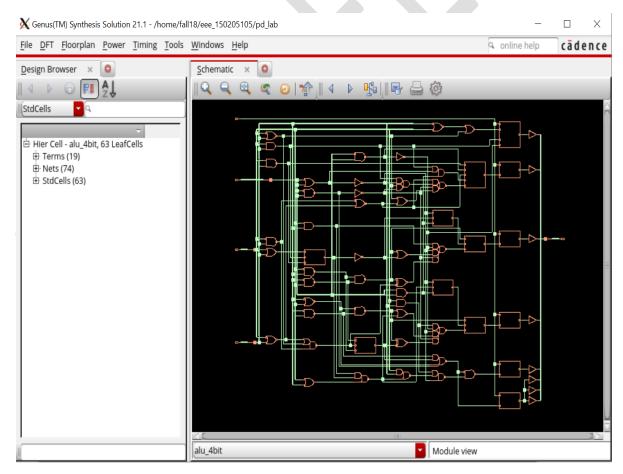

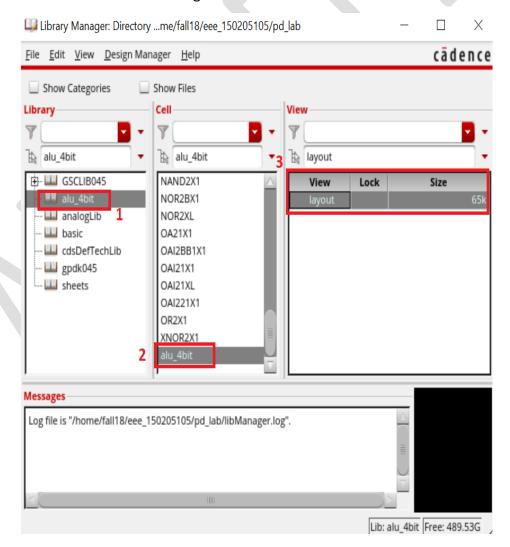

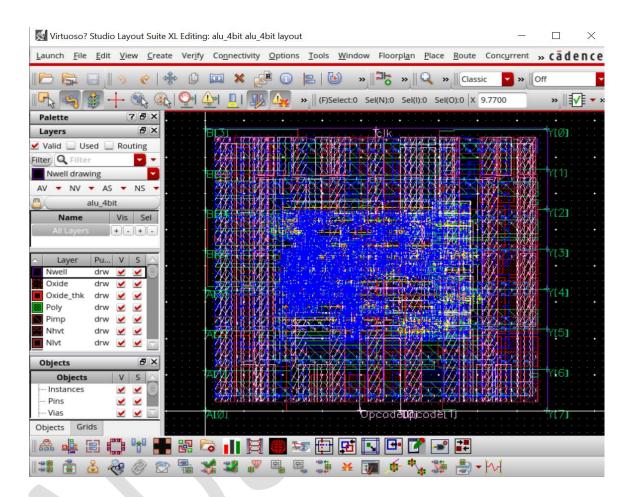

In this lab, we will perform synthesis on the RTL of a 4-bit ALU designed and verified in Lab-3 (Example 5).

- First log in to the VLSI lab server with the appropriate cadence license and launch Gnome-Terminal. [Xlaunch → putty → login → csh→ source ~/cshrc.txt→ gnome-terminal&]

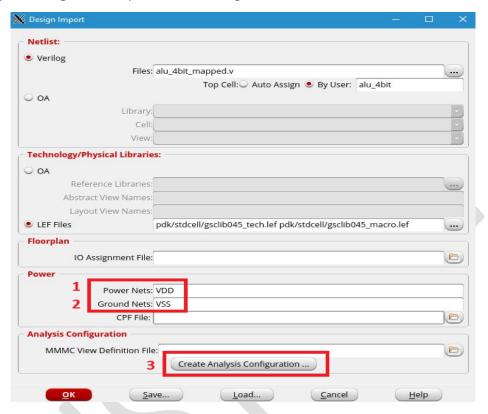

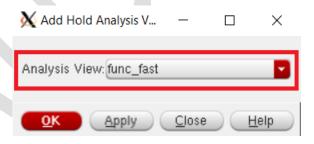

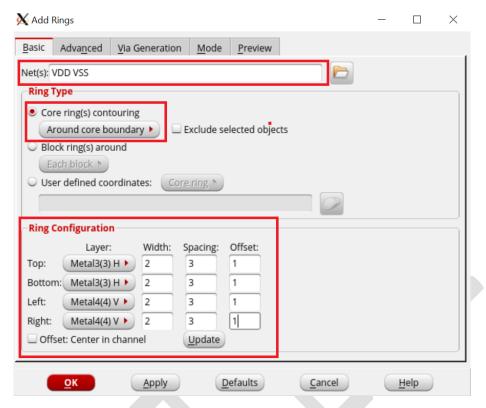

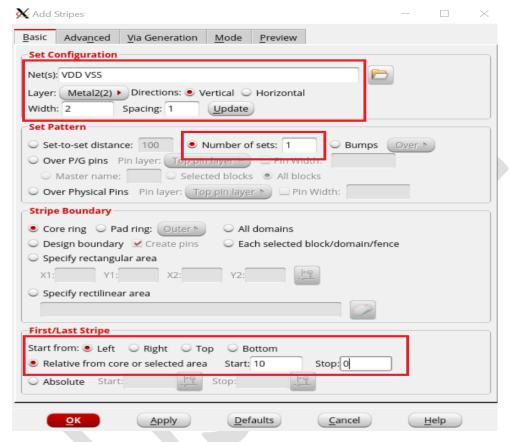

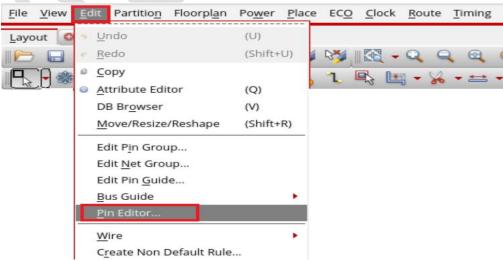

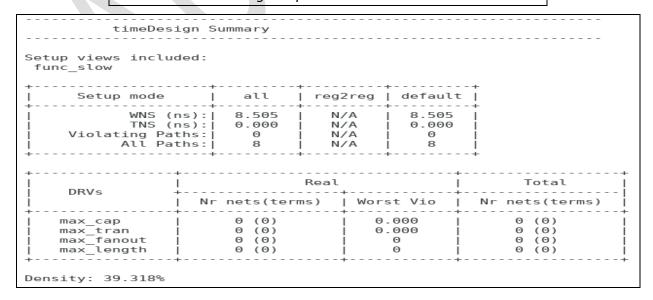

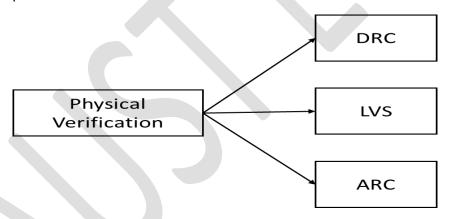

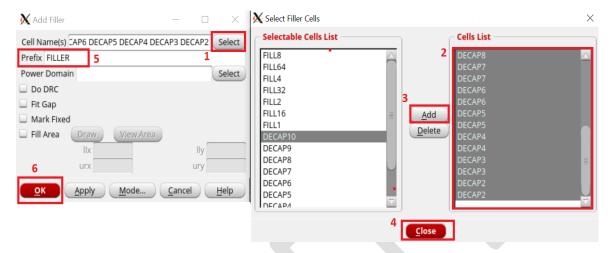

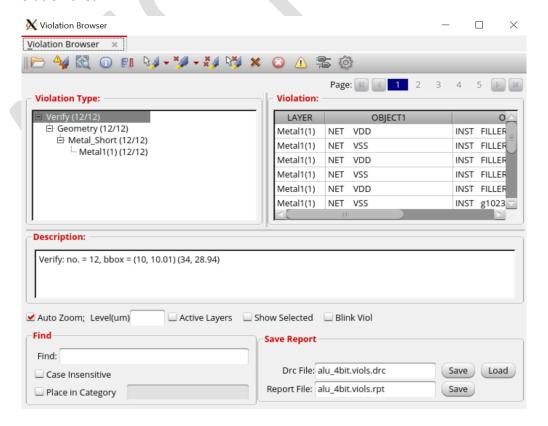

- 2. Then go to the home directory using the following command